# 3-Channel Constant-Current Sink Driver for RGB LED Clusters

### **Features**

- 3 constant-current channels for RGB each

- Output current invariant to load voltage change

- Maximum output current per channel: 60mA

- Range of constant current per channel: 5~ 60mA

- Cascading buffers for wired transmission

- Self synchronized signal timing of clock (CLK) and data (SDO)

- Low power consumption: 120mW

- Output current deviation:

between channels: < ±5% (max.), and

between ICs: < ±5% (max.)

- Sustaining voltage: 17V

- Built-in voltage regulator working with supply voltage ranging from 6.0V to 12V

- 5 MHz clock frequency at 2-meter cable transmission

- Package type: SSOP20, "Pb-free & Green" package

RGB LED clusters which are used in:

- Channel letters

- Landscape lighting

- Neon lamp alternative

### **General Description**

MBI6010 is a 3-channel constant-current sink driver for RGB LED cluster, which can be networked to a master controller for scheduled or manual dimming and color control. Each MBI6010 enhances the transmission buffers for data (SDI, SDO), clock (CLK, CLK\_OUT), latch (LE, LE\_OUT), and output enable (OE, OE\_OUT) in a cascading system by the unique "self synchronized signal timing" technology. At MBI6010 output stage, three regulated current ports are adjustable with three corresponding external resistors to match RGB color characteristics. With built-in voltage regulator, MBI6010 provides users with great supply voltage range form 6.0V to 12V, maintains constant current up from 5mA to 60mA and saves the space in a compact cluster. In addition, MBI6010 sustains 17V at output ports. This provides enhanced LED controllability and better mixed-color lighting solution.

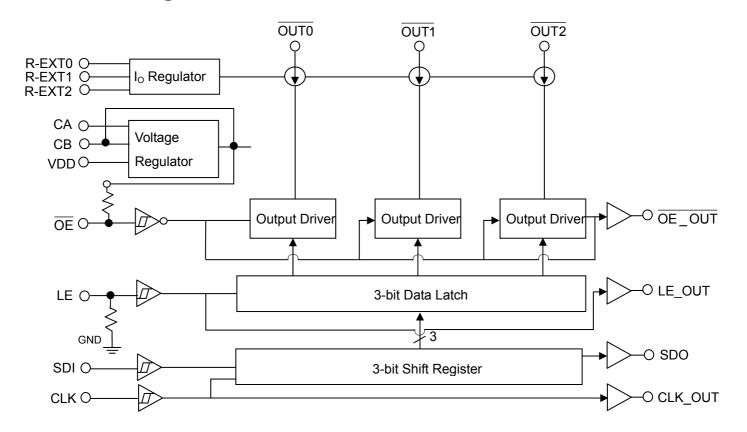

### **Functional Diagram**

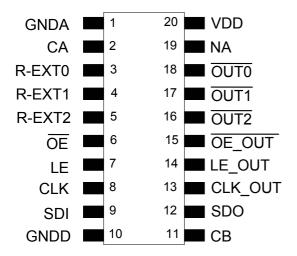

### **Pin Configuration**

# **Terminal Description**

| Pin No.  | Pin Name   | Function                                                                                                                                               |  |  |  |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | GNDA       | Analog ground                                                                                                                                          |  |  |  |

| 2        | CA         | Connected to a compensated capacitor for the regulator output.                                                                                         |  |  |  |

| 3,4,5    | R-EXT0,1,2 | Input terminal used to connect an external resistor for setting up output current for all output channels                                              |  |  |  |

|          |            | Output enable input terminal                                                                                                                           |  |  |  |

| 6        | ŌĒ         | When $\overline{OE}$ is active (low), the output ports are enabled; when $\overline{OE}$ is inactive (high), all output ports are turned off (blanked) |  |  |  |

|          |            | Data strobe input terminal                                                                                                                             |  |  |  |

| 7 LE     |            | The data in shift register is transferred to the data latch when LE is high. The data is latched when LE goes low.                                     |  |  |  |

| 8        | CLK        | Clock input terminal for data shift on rising edge                                                                                                     |  |  |  |

| 9        | SDI        | Serial data input terminal to the shift register                                                                                                       |  |  |  |

| 10       | GNDD       | Digital ground                                                                                                                                         |  |  |  |

| 11       | СВ         | Connected to a compensated capacitor for the regulator output.                                                                                         |  |  |  |

|          |            | Serial data output terminal to be connected to the SDI of the next driver IC. SDO signal changes on falling edge of CLK.                               |  |  |  |

| 13       | CLK_OUT    | Clock output terminal, CLK replica, connected to the next CLK                                                                                          |  |  |  |

| 14       | LE_OUT     | LE output terminal, LE replica, connected to the next LE                                                                                               |  |  |  |

| 15       | OE_OUT     | OE output terminal, OE replica, connected to the next OE                                                                                               |  |  |  |

| 16,17,18 | OUT0,1,2   | Constant current output terminal                                                                                                                       |  |  |  |

| 19       | NA         | Not used                                                                                                                                               |  |  |  |

| 20       | VDD        | Supply voltage terminal                                                                                                                                |  |  |  |

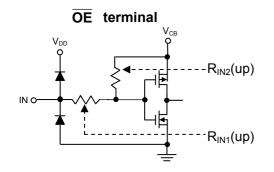

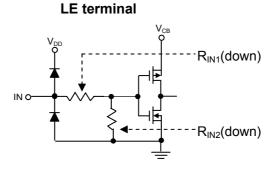

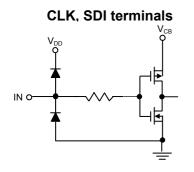

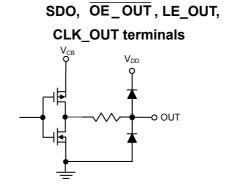

# **Equivalent Circuits of Input and Output Terminals**

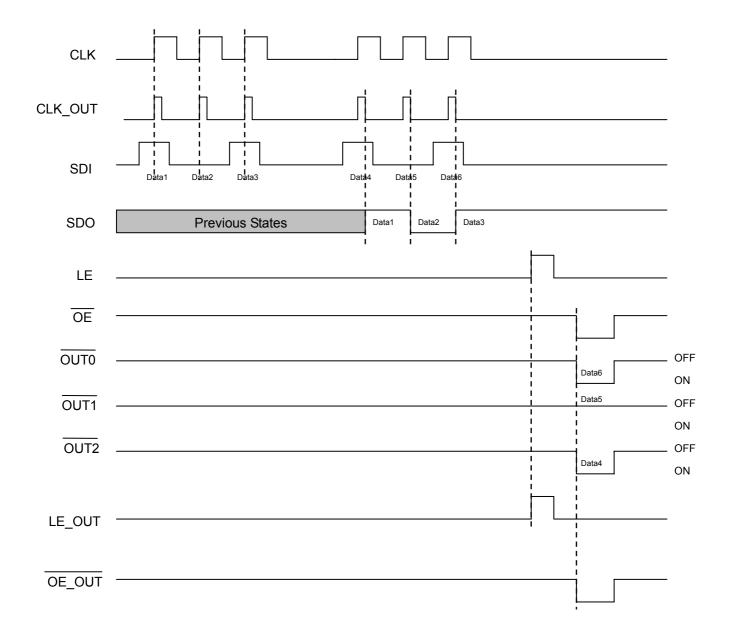

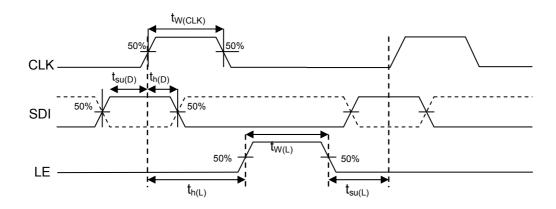

# **Timing Diagram**

# **Maximum Ratings**

| Characteristic                    | Symbol               | Rating                    | Unit |

|-----------------------------------|----------------------|---------------------------|------|

| Supply Voltage                    | $V_{DD}$             | 15                        | V    |

| Input Voltage                     | V <sub>IN</sub>      | -0.4~V <sub>DD</sub> +0.4 | V    |

| Output Current per Output Channel | I <sub>OUT</sub>     | +90                       | mA   |

| Sustaining Voltage at OUT port    | V <sub>DS</sub>      | 17.0                      | V    |

| GND Terminal Current              | I <sub>GND</sub>     | 1000                      | mA   |

| Power Dissipation at 25°C         | P <sub>D</sub>       | 1.7                       | W    |

| Thermal Resistance                | R <sub>th(j-a)</sub> | 73.43                     | °C/W |

| Operating Junction Temperature    | $T_{j,max}$          | 150                       | °C   |

| Operating Temperature             | T <sub>opr</sub>     | -40~+85                   | °C   |

| Storage Temperature               | T <sub>stg</sub>     | -55~+150                  | °C   |

### **Electrical Characteristics**

MBI6010 electrical characteristics are measured under the test conditions where TA=25°C and  $V_{DD}$ =6.0~12.0V.

| Characteristic                                                 |                                                                             | Symbol                     | Condition                                                                                 |                                                | Min. | Тур. | Max. | Unit  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------|------|------|------|-------|--|

| Supply Voltage                                                 |                                                                             | $V_{DD}$                   | -                                                                                         |                                                | 6.0  | -    | 12   | V     |  |

| Output Voltage of CA,CB                                        |                                                                             | $V_{CA}, V_{CB}$           | When V <sub>DD</sub> =12V                                                                 |                                                | 4.8  | 5.3  | 6.0  | V     |  |

| L                                                              | "H" level V <sub>IH</sub> V <sub>CB</sub> =5V under I <sub>OUT</sub> ≦0.5μA |                            | <sub>out</sub> ≦0.5µA                                                                     | 3.5                                            | -    | 12.0 | V    |       |  |

| Input Voltage                                                  | nput Voltage                                                                |                            | V <sub>CB</sub> =5V under I <sub>C</sub>                                                  | <sub>3</sub> =5V under I <sub>OUT</sub> ≦0.5µA |      | -    | 1.4  | V     |  |

| Output Current                                                 |                                                                             | I <sub>ОН</sub>            | SDO, LE_OUT, OE_OUT,<br>CLK_OUT, at V <sub>OH</sub> =3.5V<br>(refer to Fig. 2)            |                                                | -    | -20  | -    | mA    |  |

|                                                                |                                                                             | I <sub>OL</sub>            | SDO, LE_OUT, OE_OUT,<br>CLK_OUT, at V <sub>OL</sub> =1.5V<br>(refer to Fig. 2)            |                                                | -    | 20   | -    | mA    |  |

| Sustaining Vo                                                  | ltage                                                                       | $V_{\text{DS},\text{SUS}}$ | OUT0 ~ OUT2                                                                               |                                                | ı    | ı    | 17.0 | V     |  |

| Output Leaka                                                   | ge Current                                                                  | I <sub>OUT,LEAK</sub>      | V <sub>DS</sub> =17.0V                                                                    |                                                | -    | -    | 0.5  | μA    |  |

| Voltage at                                                     | SDO,<br>LE_OUT,                                                             | $V_{OL}$                   | I <sub>OL</sub> =+1.0mA                                                                   |                                                | -    | -    | 0.4  | V     |  |

| signal output<br>terminals                                     | OE_OUT,                                                                     | $V_{OH}$                   | I <sub>OH</sub> =-1.0mA (refer to V <sub>CA</sub> , V <sub>CB</sub> )                     |                                                | 4.5  | -    | -    | V     |  |

| Output Current                                                 |                                                                             | I <sub>OUT</sub>           | DC Test Circuit, OUT0 ~ OUT2                                                              |                                                | 5    | -    | 60   | mA    |  |

| Output Current 1                                               |                                                                             | I <sub>OUT1</sub>          | V <sub>DS</sub> =0.8V                                                                     | $R_{\text{ext}}$ =6K $\Omega$                  | -    | 26.0 | -    | mA    |  |

| Current Skew 1                                                 |                                                                             | dl <sub>OUT1</sub>         | I <sub>OL</sub> =25.0mA<br>V <sub>DS</sub> =0.8V                                          | R <sub>ext</sub> =6KΩ                          | -    | -    | ±6   | %     |  |

| Output Current 2                                               |                                                                             | I <sub>OUT2</sub>          | V <sub>DS</sub> =0.8V                                                                     | $R_{\text{ext}}$ =30K $\Omega$                 | -    | 5.0  | -    | mA    |  |

| Current Skew 2                                                 |                                                                             | dl <sub>OUT2</sub>         | I <sub>OL</sub> =5.0mA<br>V <sub>DS</sub> =0.8V                                           | R <sub>ext</sub> =30KΩ                         | -    | -    | ±6   | %     |  |

| Regulation of Output<br>Current vs. Voltage at<br>Output Ports |                                                                             | %/dV <sub>DS</sub>         | When V <sub>DS</sub> is within 1.0V and 3.0V                                              |                                                | -    | ±0.2 | -    | % / V |  |

| Regulation of Output<br>Current vs. Supply Voltage<br>Change   |                                                                             | %/dV <sub>DD</sub>         | When V <sub>DD</sub> is within 6.0V and 12.0V                                             |                                                | -    | ±1.0 | -    | % / V |  |

| Voltage at R-EXT0,<br>R-EXT1, R-EXT2 pins                      |                                                                             | $V_{REXT}$                 | When V <sub>DD</sub> is within 6.0V and 12.0V                                             |                                                | 1.2  | 1.24 | 1.3  | V     |  |

| Pull-up Resistor                                               |                                                                             | R <sub>IN</sub> (up)       | $\overline{OE}$ , $R_{IN}(up) = R_{IN1}(up) + R_{IN2}(up)$                                |                                                | 400  | 700  | 1000 | ΚΩ    |  |

| Pull-down Resistor                                             |                                                                             | R <sub>IN</sub> (down)     | LE, $R_{IN}(down) = R_{IN1}(down) + R_{IN2}(down)$                                        |                                                | 400  | 700  | 1000 | ΚΩ    |  |

| Supply<br>Current                                              | "OFF"                                                                       | I <sub>DD</sub> (off) 1    | R <sub>ext</sub> =Open, OU                                                                | IT0~OUT2=Off                                   | -    | 4    | 7    |       |  |

|                                                                |                                                                             | I <sub>DD</sub> (off) 2    | $R_{\text{ext}}$ =6K $\Omega$ , $\overline{OL}$                                           | JT0~OUT2=Off                                   | -    | 5    | 8    |       |  |

|                                                                |                                                                             | I <sub>DD</sub> (off) 3    |                                                                                           | JT0~OUT2=Off                                   | -    | 7    | 10   | mA    |  |

|                                                                | "ON"                                                                        | I <sub>DD</sub> (on) 1     |                                                                                           | JT0~OUT2=On                                    | -    | 5    | 8    | ] '   |  |

|                                                                |                                                                             | I <sub>DD</sub> (on) 2     | $R_{\text{ext}}$ =30K $\Omega$ , $\overline{\text{OUT0}} \sim \overline{\text{OUT2}}$ =On |                                                | -    | 7    | 10   |       |  |

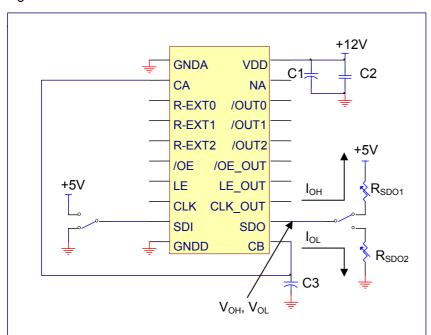

### **Test Circuit for Electrical Characteristics**

Figure 1

Figure 2

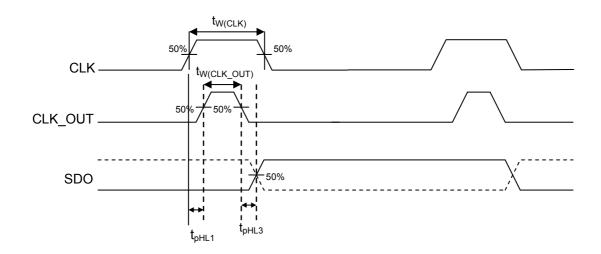

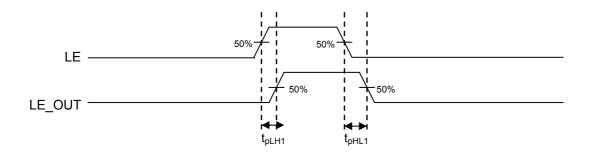

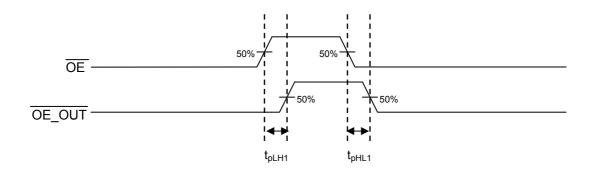

# **Switching Characteristics**

| Characteristic             |                                           | Symbol                                  | Condition                                                                                                                                                                 | Min. | Тур. | Max. | Unit |

|----------------------------|-------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Delay time<br>("L" to "H") | OE - OE _ OUT<br>LE-LE_OUT<br>CLK-CLK_OUT | t <sub>pLH1</sub>                       |                                                                                                                                                                           | -    | 20   | 30   | ns   |

|                            | OE_OUT ₀                                  | t <sub>pLH2</sub>                       |                                                                                                                                                                           | -    | 100  | 150  | ns   |

| Delay Time                 | OE - OE_OUT<br>LE-LE_OUT                  | t <sub>pHL1</sub>                       |                                                                                                                                                                           | -    | 20   | 30   | ns   |

| ("H" to "L")               | OE_OUT ₀                                  | t <sub>pHL2</sub>                       |                                                                                                                                                                           | -    | 100  | 150  | ns   |

|                            | CLK_OUT-SDO                               | t <sub>pHL3</sub>                       |                                                                                                                                                                           | _    | 5    | 20   | ns   |

| Pulse Width                | CLK_OUT                                   | t <sub>w(CLK_OUT)</sub>                 |                                                                                                                                                                           | 30   | 40   | 50   | ns   |

| Stagger Delay<br>Time      | Output Ports                              | ts                                      | T <sub>A</sub> =25°C                                                                                                                                                      | -    | 80   | -    | ns   |

|                            | OE_OUT                                    | $t_{r(OE)}$                             | $V_{DD}$ =12V<br>$V_{DS}$ =1V<br>$V_{IH}$ =VDD<br>$V_{IL}$ =GND<br>$R_{ext}$ =7.5K $\Omega$<br>$(I_{OUT}$ =20mA)<br>$V_{L}$ =5V<br>$R_{L}$ =150 $\Omega$<br>$C_{L}$ =10pF | -    | 3    | 10   | ns   |

|                            | LE_OUT                                    | $t_{r(LE)}$                             |                                                                                                                                                                           | -    | 3    | 10   | ns   |

| Rise Time                  | CLK_OUT                                   | t <sub>r(CLK)</sub>                     |                                                                                                                                                                           | _    | 5    | 10   | ns   |

|                            | SDO                                       | t <sub>r(SDO)</sub>                     |                                                                                                                                                                           | -    | 5    | 10   | ns   |

|                            | Output Ports                              | t <sub>or</sub>                         |                                                                                                                                                                           | -    | 180  | 220  | ns   |

|                            | OE_OUT                                    | $t_{f(OE)}$                             |                                                                                                                                                                           | -    | 3    | 10   | ns   |

|                            | LE_OUT                                    | $t_{f(LE)}$                             |                                                                                                                                                                           | -    | 3    | 10   | ns   |

| Fall Time                  | CLK_OUT                                   | t <sub>f(CLK)</sub>                     |                                                                                                                                                                           | _    | 5    | 10   | ns   |

|                            | SDO                                       | t <sub>f(SDO)</sub>                     |                                                                                                                                                                           | -    | 5    | 10   | ns   |

|                            | Output Ports                              | t <sub>of</sub>                         |                                                                                                                                                                           | -    | 60   | 100  | ns   |

| Hold Time                  | LE                                        | t <sub>h(L)</sub>                       |                                                                                                                                                                           | 5    | -    | -    | ns   |

| Tiola Tillie               | SDI                                       | t <sub>h(D)</sub>                       |                                                                                                                                                                           | 10   | -    | -    | ns   |

| Setup Time                 | LE                                        | t <sub>su(L)</sub>                      | -                                                                                                                                                                         | 25   | -    | -    | ns   |

|                            | SDI                                       | t <sub>su(D)</sub>                      |                                                                                                                                                                           | 5    | -    | -    | ns   |

| Pulse Width                | ŌĒ                                        | $t_{w(OE)}$                             |                                                                                                                                                                           | 5*   | -    | -    | μs   |

|                            | LE                                        | t <sub>w(L)</sub>                       |                                                                                                                                                                           | 50   | -    | -    | ns   |

|                            | CLK                                       | t <sub>w(CLK)</sub><br>F <sub>CLK</sub> |                                                                                                                                                                           | 30   | -    | -    | ns   |

| Frequency                  |                                           |                                         | _                                                                                                                                                                         | -    | -    | 5    | MHz  |

| Maximum CLK Rise Time      |                                           | t <sub>r</sub>                          |                                                                                                                                                                           | _    | -    | 500  | ns   |

| Maximum CLK Fall Time      |                                           | t <sub>f</sub>                          |                                                                                                                                                                           | -    | -    | 500  | ns   |

<sup>\*</sup>When  $\overline{\text{OE}}$  > 5µs, the deviation of the turn-on time of OUT0, OUT1, OUT2 is negligible.

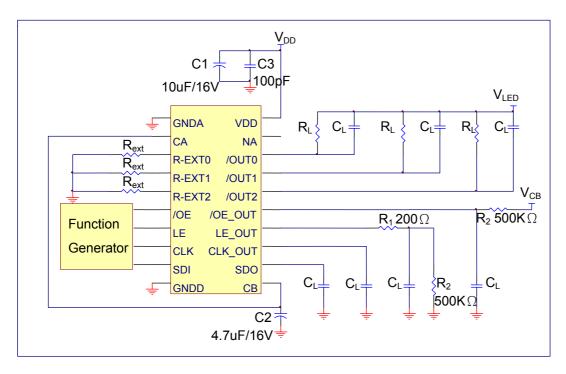

# **Test Circuit for Switching Characteristics**

Figure 3

# **Timing Waveform**

### **Application Information**

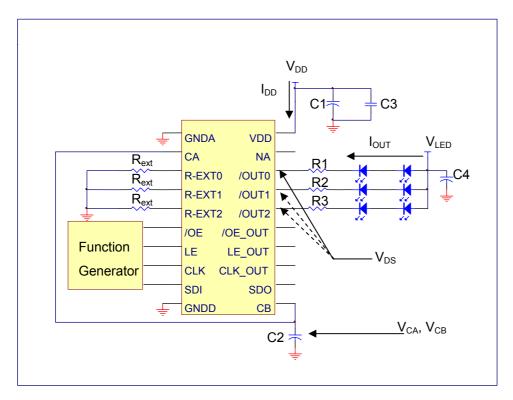

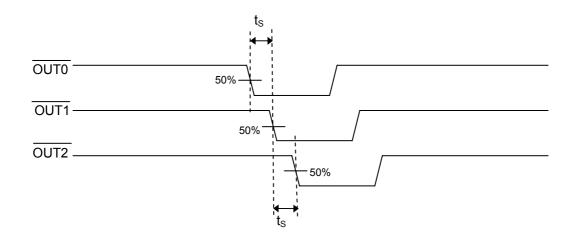

### **Application Circuit\***

Figure 4

- \* For detailed circuit information, please refer to the MBI6010 Application Note.

- \*\* When the  $R_{ext}$  is 7.5k $\Omega$ , the  $I_{OUT}$  is 20mA.

- \*\*\*C1~C6 are required. The values of the C1/C4 and C3/C6 are for reference only. The value of C2/C5 ranges from

- 4.7uF/16V to 10uF/16V. Tantalum capacitors or capacitors with ESR < 2  $\Omega$  are recommended.

- \*\*\*\*C7~C22 and R7~R22 can modify the signal waveforms. For detailed information, please refer to the MBI6010 Application Note.

### **Constant Current**

In LED display application, MBI6010 provides nearly no variation in current from channel to channel and from IC to IC. This can be achieved by:

- 1) The maximum current variation between channels is less than  $\pm 5\%$ , and that between ICs is less than  $\pm 5\%$ .

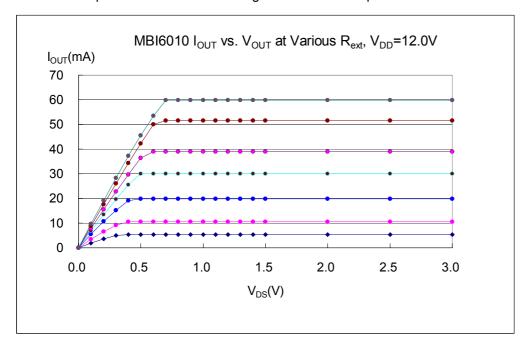

- 2) In addition, the current characteristic of output stage is flat and users can refer to the figure as shown below. The output current can be kept constant regardless of the variations of LED forward voltages (V<sub>F</sub>). This guarantees LED to be performed on the same brightness as user's specification.

Figure 5

### **Setting Output Current**

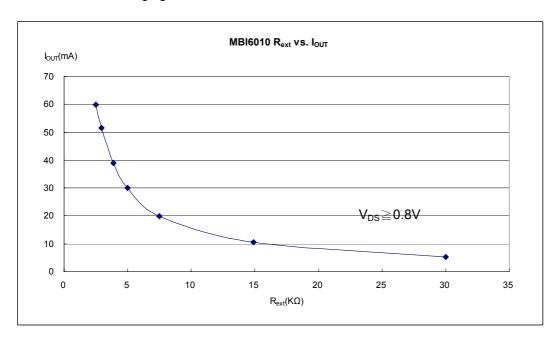

The output current of each channel ( $I_{OUT}$ ) is set by an external resistor,  $R_{ext}$ . The relationship between  $I_{OUT}$  and  $R_{ext}$  is shown in the following figure.

Figure 6

Also, the output current can be calculated from the equation:

I<sub>OUT</sub>=V<sub>REXT</sub> / R<sub>ext</sub> \*120;

V<sub>REXT</sub>= 1.24V;

where  $R_{ext}$  is the resistance of the external resistor connected to R-EXT terminal. The magnitude of current (as a function of  $R_{ext}$ ) is around 60mA at 2.5K $\Omega$  and 20mA at 7.5K $\Omega$ .

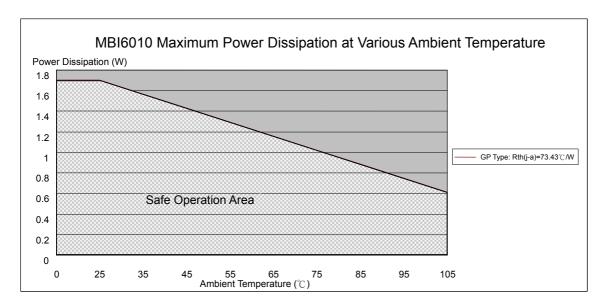

### Package Power Dissipation (P<sub>D</sub>)

The maximum power dissipation,  $P_D(max)=(T_{i,max}-T_a)/R_{th(i-a)}$ , decreases as the ambient temperature increases.

Figure 7

### Load Supply Voltage (V<sub>LED</sub>)

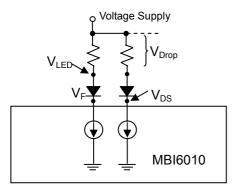

MBI6010 is designed to operate with adequate  $V_{DS}$  to achieve constant current.  $V_{DS}$  together with  $I_{OUT}$  should not exceed the package power dissipation limit,  $P_{D(max)}$ .

As in Figure 8,  $V_{DS} = V_{LED} - V_F$ , and  $V_{LED}$  is the load supply voltage.  $P_{D(act)}$  will be greater than  $P_{D(max)}$ , if  $V_{DS}$  drops too much voltage on the driver. In this case, it is recommended to use the lowest possible supply voltage or to set an external voltage reducer, VDROP.

A voltage reducer lets  $V_{DS} = (V_{LED} - V_F) - V_{DROP}$ .

Resistors can be used in the applications as shown in Figure 8.

Figure 8

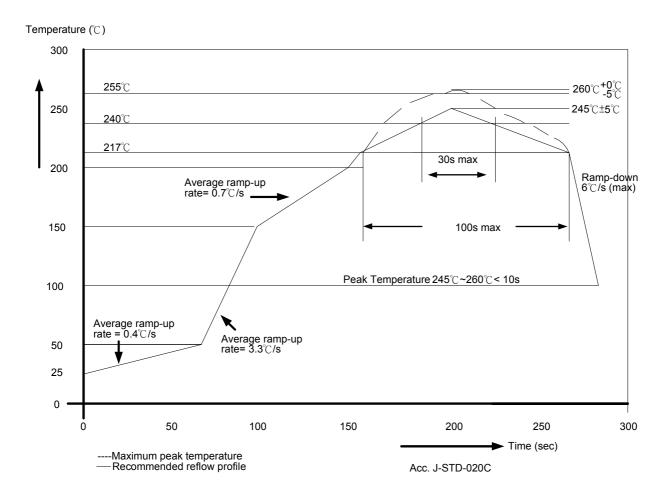

### Soldering Process of "Pb-free & Green" Package Plating\*

Macroblock has defined "Pb-Free & Green" to mean semiconductor products that are compatible with the current RoHS requirements and selected 100% pure tin (Sn) to provide forward and backward compatibility with both the current industry-standard SnPb-based soldering processes and higher-temperature Pb-free processes. Pure tin is widely accepted by customers and suppliers of electronic devices in Europe, Asia and the US as the lead-free surface finish of choice to replace tin-lead. Also, it is backward compatible to standard 215°C to 240°C reflow processes which adopt tin/lead (SnPb) solder paste. However, in the whole Pb-free soldering processes and materials, 100% pure tin (Sn) will all require up to 260°C for proper soldering on boards, referring to J-STD-020C as shown below.

\*Note: For details, please refer to Macroblock's "Policy on Pb-free & Green Package".

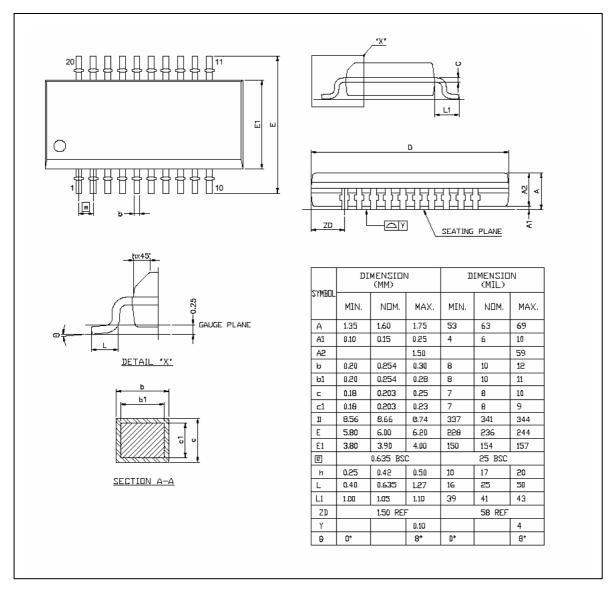

# **Package Outline**

MBI6010GP Outline Drawing

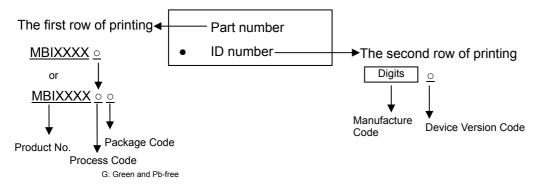

### **Product Top-mark Information**

### **Product Revision History**

| Datasheet Version | Device Version Code |

|-------------------|---------------------|

| V1.00             | Α                   |

# **Product Ordering Information**

| Part Number | Package Type    | Weight (g) | Minimum Order Quantity (Pieces per Reel) |

|-------------|-----------------|------------|------------------------------------------|

| MBI6010GP   | SSOP20-150-0.65 | 0.635      | -                                        |